# Moore's Law Effect on Transistors Evolution

Sabeen Rashid<sup>1</sup>, Rabia Shakeel<sup>1</sup>, Huma Bashir<sup>1</sup>, Khadija Malik<sup>1</sup>, Kainat Wajib<sup>1</sup> <sup>1</sup>Department of Computer Science, Abdul Wali Khan University Mardan, Pakistan

**Abstract**-With respect to time increasing in the number of transistors has a great effect on the performance and the speed of processors. In this paper we are comparing the transistors evolution related to Moore's law. According to the Moore's law the number of transistors should be double every 24 month. The effect of increasing processors design complexity also increases the power consumption and cost of design efforts. In this paper we discuss the methods and procedures to scale the hardware complexity of processors.

Keywords: Hardware Complexity, Processor Design, Transistor Count, Moore's Law.

### I. INTRODUCTION

The MOORE's law observations states that the number of transistors are doubling every two years. More precisely within the period of "18 months" is due to Intel executive David House, the increase in number of transistors and increase in speed of transistors give rise to the effect of increase in the performance of the transistors. Moore's law has its same effect during the history of semiconductor since the advent of computing devices to now mobile devices, a continuous improvement of silicon chips [1-6]. The two factors have made a great impact on the success of Moore's law, consumers demand for more functionality and the competition among the developers.

The technology has improved, better to call it as evaluated from mid-1970's 6800 processor with 5000 transistors to the today's multicore processors like reaching the limit of 3 billion. The fact about Moore's law is to improve those area that helps to achieve the more and more small sized transistors and with more better technology

#### II. BACKGROUND

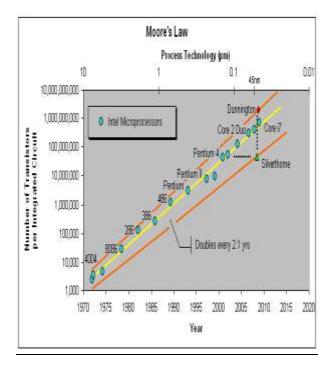

Moore's law state that transistor numbers become two times in every 18 to 24 months in article. "Cramming more components onto integrated circuits", *Electronics Magazine* 19 April 1965: The transistor cost has become double in every 24 months and this is remaining increasing at least at this order, if no chance of increase more. For many years of gap the speed of increase became very low so we can say that there are no observable changes in period of 10 years. During the year of 1975 the transistor cost on each integrated circuit is atleast 65000. So clearly I am sure about that one wafer can adjust one integrated circuit [2]. The statement of Moore's that number of transistor on integrated circuit will becomes two times in a period of every 18 to 24 months. The statement is given by scientist named as Golden Moore in 1965. The law is still useful and applicable. It is the high demand of small sized. low

Power consumption and higher processing speed transistors that have prolonged the life of Moore's Law, and until now Moore's Law is still used as the guideline for transistor manufacturing. The Moore's Law graph is shown in Figure 1.

Figure 1. Moore's Law Graph

During the period of 1970s more electronics were built as compared to the previous years as industry was more than doubling the total number of transistors. The transistors capacity has continuously getting better. Moore's law rating has recently slowed but still on a good growth. Todays a number of transistors in one year is up to 10^18. According to a well-known naturalist Edward O. Wilson, at Harvard, had counted that they were approximately10^16 and 10^17 ants on earth. In 1990s then the semiconductor industry was producing a transistor for every ant. Now, the poor little ant has to carry a hundred of them [7-9] around if he is going to get his share.

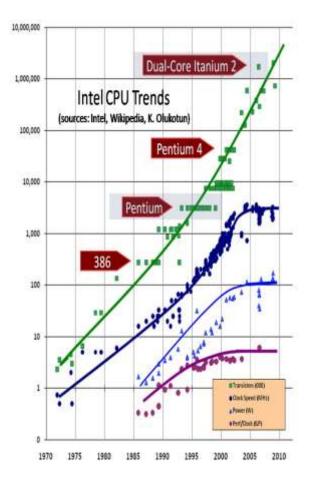

Processor speeds from the 1970's to 2009 and then again in 2010, one may think [10-19] that the law has reached its limit or is nearing the limit. In the 1970's processor speeds ranged from 740 KHz to 8MHz; notice that the 740 is KHz, which is Kilo Hertz – while the 8 is MHz, which is Mega Hertz.

From 2000 - 2009 there has not really been much of a speed difference as the speeds range from 1.3 GHz to 2.8 GHz, which suggests that the speeds have barely doubled within a 10 year span. This is because we are looking at the speeds and not the number of transistors; in 2000 the number of transistors in the CPU numbered 37.5 million, while in 2009 the number went up to an outstanding 904 million; this is why it is more accurate to apply the law to transistors than to speed [20].

From all of the above discussion about transistors ,every computer literate person can't drawn result from it easily [21-25] so we say that earlier processors used one CPU while todays processors are multicore technology using more than one CPU,s.

In example above the speed of the CPU during many years of gap increase from 1.3 to 2.8 which is speed of a single CORE, QUAD CORE processors.in conclusion we can say that power of 2.8 is obtain if multiply it with four which is 11.2 this is very large from 1.3.

# III. CHALLENGES INCURRED

There is an inflection point to the technology of semiconductors. Table 1 below, shows some serious challenges faced by semiconductor technology .More and smaller transistors are not always "better". Second denard scaling also has ended, power per transistor is not good [26-33]. Third, challenge is fabrication variations subject to the reliability of transistors (nano-scale features e.g., gate oxides only atoms thick). Fourth, communication among computation elements must be managed through locality to achieve goals at acceptable cost and energy with new opportunities (e.g., chip stacking) and new challenges (e.g., data centers). Fifth, for achieving high performance, costs to create, design, verify, fabricate, and test are growing, making them harder to afford.

Table 1: Technology's Challenges to Computer Architecture

| 1970s                                                                                   | Newer trend                                                                  |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Double transistors<br>per chip_ in<br>every 18-24 months                                | Transistor count still 2× every 18-<br>24 months,                            |

| Dennard<br>Scaling(power per<br>transistor) — near-<br>constant<br>power/chip           | Not viable for power/chip to<br>double (with 2×<br>transistors/chip growth)  |

| The modest levels<br>of transistor<br>unreliability easily<br>hidden (e.g., via<br>ECC) | Transistor reliability is going to be effected                               |

| Focus on<br>computation over<br>communication                                           | Restricted communication<br>communication more expensive<br>than computation |

| One-time creation<br>of very high<br>performance and<br>reliability is difficult        | Expensive to design, verify, fabricate, and test                             |

# IV. INCREASING THE NUMBER OF TRANSISTORS

Many limitations are still there, such as increasing the density size, the die size, physical size decrement, the voltage [34].

Since the surface area of a transistor determines the transistor count per square millimeter of silicon, and as the feature size is decreasing transistors density increases quadratically. And as the surface area of a transistor determines the transistor count per square millimeter of silicon [35]. The increase in transistor performance is more complicated As the physical size is decreased. A reduction in operating voltage to maintain correct operation and reliability of the transistor is required in the vertical dimension shrink. This combination [36-39] of scaling factors leads to a complex interrelationship between the transistor performance and the process feature size and it makes difficult to apply Moore's Law in the future. Some studies have shown that physical limitations could be reached by 2018 [7] or 2020-2022[8, 9, 10, 11].

Processor's hardware complexity is caused by doubling the number [40-47] of transistors every two years (see Table 2), which will be limited after a few years [12, 13, 14, 15].

## V. CONCLUSION

Although clock speeds and transistors per circuit have not kept pace with the original exponential forecast known as Moore's Law, doubling every year, computing performance and cost efficiencies continue to advance at a remarkable pace. Competition among the major processor manufacturers, Intel, AMD, IBM, Sun, and Texas Instruments can be expected to push the industry down the long-run average total cost curves described by Gordon Moore in 1965. As he predicted, the result will be dramatic improvements and much lower prices for computing performance. While clock speeds may continue to be a standard measure of performance.

#### REFERENCE

- Khan, F., Bashir, F., & Nakagawa, K. (2012). Dual Head Clustering Scheme in Wireless Sensor Networks. in the IEEE International Conference on Emerging Technologies (pp. 1-8). Islamabad: IEEE Islamabad.

- [2]. M. A. Jan, P. Nanda, X. He, Z. Tan and R. P. Liu, "A robust authentication scheme for observing resources in the internet of things environment" in 13th International Conference on Trust, Security and

Privacy in Computing and Communications (TrustCom), pp. 205-211, 2014, IEEE.

- [3]. Khan, F., & Nakagawa, K. (2012). Performance Improvement in Cognitive Radio Sensor Networks. in the Institute of Electronics, Information and Communication Engineers (IEICE), 8.

- [4]. M. A. Jan, P. Nanda and X. He, "Energy Evaluation Model for an Improved Centralized Clustering Hierarchical Algorithm in WSN," in Wired/Wireless Internet Communication, Lecture Notes in Computer Science, pp. 154–167, Springer, Berlin, Germany, 2013.

- [5]. Khan, F., Kamal, S. A., & Arif, F. (2013). Fairness Improvement in long-chain Multi-hop Wireless Adhoc Networks. International Conference on Connected Vehicles & Expo (pp. 1-8). Las Vegas: IEEE Las Vegas, USA.

- [6]. M. A. Jan, P. Nanda, X. He and R. P. Liu, "Enhancing lifetime and quality of data in cluster-based hierarchical routing protocol for wireless sensor network", 2013 IEEE International Conference on High Performance Computing and Communications & 2013 IEEE International Conference on Embedded and Ubiquitous Computing (HPCC & EUC), pp. 1400-1407, 2013.

- [7]. Q. Jabeen, F. Khan, S. Khan and M.A Jan. (2016). Performance Improvement in Multihop Wireless Mobile Adhoc Networks. *in the Journal Applied*, *Environmental, and Biological Sciences (JAEBS)*, vol. 6(4S), pp. 82-92. Print ISSN: 2090-4274 Online ISSN: 2090-4215, TextRoad.

- [8]. Khan, F., & Nakagawa, K. (2013). Comparative Study of Spectrum Sensing Techniques in Cognitive Radio Networks. in IEEE World Congress on Communication and Information Technologies (p. 8). Tunisia: IEEE Tunisia.

- [9]. Khan, F. (2014). Secure Communication and Routing Architecture in Wireless Sensor Networks. the 3<sup>rd</sup> Global Conference on Consumer Electronics (GCCE) (p. 4). Tokyo, Japan: IEEE Tokyo.

- [10]. M. A. Jan, P. Nanda, X. He and R. P. Liu, "PASCCC: Priority-based application-specific congestion control clustering protocol" Computer Networks, Vol. 74, PP-92-102, 2014.

- [11]. Khan, F. (2014, May). Fairness and throughput improvement in multihop wireless ad hoc networks. In *Electrical and Computer Engineering (CCECE)*, 2014 IEEE 27th Canadian Conference on (pp. 1-6). IEEE.

- [12]. Mian Ahmad Jan and Muhammad Khan, "A Survey of Cluster-based Hierarchical Routing Protocols", in IRACST–International Journal of Computer Networks and Wireless Communications (IJCNWC), Vol.3, April. 2013, pp.138-143.

- [13]. Khan, S., Khan, F., & Khan, S.A.(2015). Delay and Throughput Improvement in Wireless Sensor and Actor Networks. 5th National Symposium on Information Technology: Towards New Smart World

(NSITNSW) (pp. 1-8). Riyadh: IEEE Riyad Chapter.

- [14]. Khan, F., Khan, S., & Khan, S. A. (2015, October). Performance improvement in wireless sensor and actor networks based on actor repositioning. In 2015 International Conference on Connected Vehicles and Expo (ICCVE) (pp. 134-139). IEEE.

- [15]. Khan, S., Khan, F., Jabeen, Q., Arif, F., & Jan, M. A. (2016). Performance Improvement in Wireless Sensor and Actor Networks. in the Journal Applied, Environmental, and Biological Sciences Print ISSN: 2090-4274 Online ISSN: 2090-4215

- [16]. Mian Ahmad Jan and Muhammad Khan, "Denial of Service Attacks and Their Countermeasures in WSN", in IRACST–International Journal of Computer Networks and Wireless Communications (IJCNWC), Vol.3, April. 2013.

- [17]. M. A. Jan, P. Nanda, X. He and R. P. Liu, "A Sybil Attack Detection Scheme for a Centralized Clusteringbased Hierarchical Network" in Trustcom/BigDataSE/ISPA, Vol.1, PP-318-325, 2015, IEEE.

- [18]. Jabeen, Q., Khan, F., Hayat, M.N., Khan, H., Jan., S.R., Ullah, F., (2016) A Survey : Embedded Systems Supporting By Different Operating Systems in the International Journal of Scientific Research in Science, Engineering and Technology(IJSRSET), Print ISSN : 2395-1990, Online ISSN : 2394-4099, Volume 2 Issue 2, pp.664-673.

- [19]. Syed Roohullah Jan, Syed Tauhid Ullah Shah, Zia Ullah Johar, Yasin Shah, Khan, F., " An Innovative Approach to Investigate Various Software Testing Techniques and Strategies", International Journal of Scientific Research in Science, Engineering and Technology(IJSRSET), Print ISSN : 2395-1990, Online ISSN : 2394-4099, Volume 2 Issue 2, pp.682-689, March-April 2016. URL : http://ijsrset.com/IJSRSET1622210.php

- [20]. Khan, F., Jan, SR, Tahir, M., & Khan, S., (2015) Applications, Limitations, and Improvements in Visible Light Communication Systems" In 2015 International Conference on Connected Vehicles and Expo (ICCVE) (pp. 259-262). IEEE.

- [21]. Syed Roohullah Jan, Khan, F., Muhammad Tahir, Shahzad Khan, (2016) "Survey: Dealing Non-Functional Requirements At Architecture Level", VFAST Transactions on Software Engineering, (Accepted 2016)

- [22]. M. A. Jan, "Energy-efficient routing and secure communication in wireless sensor networks," Ph.D. dissertation, 2016.

- [23]. M. A. Jan, P. Nanda, X. He, and R. P. Liu, "A Lightweight Mutual Authentication Scheme for IoT Objects," *IEEE Transactions on Dependable and Secure Computing (TDSC)*, "Submitted", 2016.

- [24]. M. A. Jan, P. Nanda, X. He, and R. P. Liu, "A Sybil Attack Detection Scheme for a Forest Wildfire Monitoring Application," *Elsevier Future Generation Computer Systems (FGCS)*, "Accepted", 2016.

- [25]. Puthal, D., Nepal, S., Ranjan, R., & Chen, J. (2015, August). DPBSV--An Efficient and Secure Scheme for Big Sensing Data Stream. InTrustcom/BigDataSE/ISPA, 2015 IEEE (Vol. 1, pp. 246-253). IEEE.

- [26]. Puthal, D., Nepal, S., Ranjan, R., & Chen, J. (2015). A Dynamic Key Length Based Approach for Real-Time Security Verification of Big Sensing Data Stream. In Web Information Systems Engineering–WISE 2015 (pp. 93-108). Springer International Publishing.

- [27]. Puthal, D., Nepal, S., Ranjan, R., & Chen, J. (2016). A dynamic prime number based efficient security mechanism for big sensing data streams. Journal of Computer and System Sciences.

- [28]. Puthal, D., & Sahoo, B. (2012). Secure Data Collection & Critical Data Transmission in Mobile Sink WSN: Secure and Energy efficient data collection technique.

- [29]. Puthal, D., Sahoo, B., & Sahoo, B. P. S. (2012). Effective Machine to Machine Communications in Smart Grid Networks. ARPN J. Syst. Softw.© 2009-2011 AJSS Journal, 2(1), 18-22.

- [30]. M. A. Jan, P. Nanda, M. Usman, and X. He, "PAWN: A Payload-based mutual Authentication scheme for Wireless Sensor Networks," "accepted", 2016.

- [31]. M. Usman, M. A. Jan, and X. He, "Cryptographybased Secure Data Storage and Sharing Using HEVC and Public Clouds," *Elsevier Information sciences*, "accepted", 2016.

- [32]. Jan, S. R., Khan, F., & Zaman, A. THE PERCEPTION OF STUDENTS ABOUT MOBILE LEARNING AT UNIVERSITY LEVEL. NO. CONTENTS PAGE NO., 97.

- [33]. Khan, F., & Nakagawa, K. (2012). B-8-10 Cooperative Spectrum Sensing Techniques in Cognitive Radio Networks. 電子情報通信学会ソサイエティ大会講 演論文集, 2012(2), 152.

- [34]. Safdar, M., Khan, I. A., Ullah, F., Khan, F., & Jan, S. R. Comparative Study of Routing Protocols in Mobile Adhoc Networks.

- [35]. Shahzad Khan, Fazlullah Khan, Fahim Arif, Qamar Jabeen, M.A Jan and S. A Khan (2016). "Performance Improvement in Wireless Sensor and Actor Networks", Journal of Applied Environmental and Biological Sciences, Vol. 6(4S), pp. 191-200, Print ISSN: 2090-4274 Online ISSN: 2090-4215, TextRoad.

- [36]. M. Usman, M. A. Jan, X. He and P. Nanda, "Data Sharing in Secure Multimedia Wireless Sensor Networks," in 15th IEEE International Conference on Trust, Security and Privacy in Computing and Communications (IEEE TrustCom-16), "accepted", 2016.

- [37]. "Moore's Law to roll on for another decade" (http://news.cnet.com/2100-1001-984051.html). . Retrieved 2011-11-27. "Moore also affirmed he never said transistor count would double every 18 months, as is commonly said. Initially, he said transistors on a chip would double every year. He then recalibrated it to every two years in 1975. David House, an Intel

executive at time, noted that the changes would cause computer performance to double every 18 months.

- [38]. Moore, Gordon E. (1965). "Cramming more components onto integrated circuits" (http://download.intel.com/museum/Moores\_Law/ Articles-Press\_Releases/Gordon\_Moore1965\_Article.pdf) (PDF). Electronics Magazine. p. 4. . Retrieved 2006-11-11`

- [39]. Robert W. Keyes, "Physical limits of silicon transistors and circuits", September 2005.

- [40]. F. Morals, L. Torres, M. Robert, D. Auvergne, "Estimation of layout densities for CMOS digitalcircuits", Proceeding International Workshop on Power and Timing Modeling Optimization Simulation (PATMOS'98), pp. 61-70, November 1998, Lyngby, Danemark.

- [41]. John L. Hennessy and David A. Patterson, "Computer Architecture, A Quantitative Approach", 5thed., pp. 17-26, 2011.

- [42]. Jan M. Rabaey, "Design at the end of Silicon Roadmap", Keynotes Address III, University of California, Berkelev, IEEE, ASP-DAC 2005.

- [43]. Ahmad, Khaled; Schuegraf, Klaus, "Transistor Wars: Rival architecture face off in a bid to keep Moore's Law-alive", IEEE Spectrum: 50, November 2011.

- [44]. Brooke Crothers, "End of Moore's Law: it's not just about physics", August 28, 2013.

- [45]. Robert Colwell, "The Chip Design Game at the End of Moore's Law", Hot Chips, August 2013.http://news.cnet.com/8301-1001\_3-57600373-92/end-of-moores-law-its-not-just-about-physics/

- [46]. Joel Hruska, "Intel's former chief architect: Moore's law will be dead within a decade", August 30, 2013.

- [47]. Pradip Bose David H. Albonesi Diana Marculescu, "Complexity-Effective Design", Proceeding International Workshop on Complexity-Effective Design, Madison, Wisconsin, June 5, 2005.